Clock Distribution In Fpga . a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. First, 16 clocks would consume too much of the available clock routing. clock networks play a vital role in ensuring uniform distribution of clock signals. these clocks present several problems. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. The internal plls provide clock. Optimizing clock networks in fpga design involves several.

from colinoflynn.com

these clocks present several problems. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. First, 16 clocks would consume too much of the available clock routing. Optimizing clock networks in fpga design involves several. The internal plls provide clock. clock networks play a vital role in ensuring uniform distribution of clock signals.

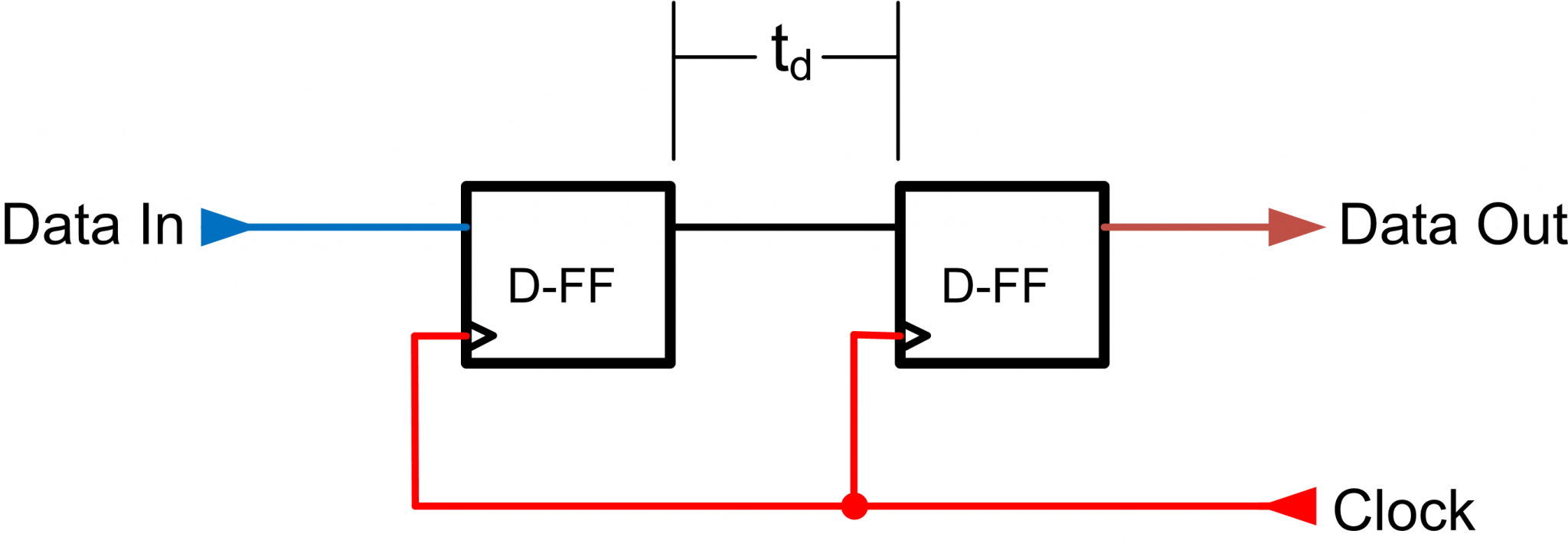

Experimenting with Metastability and Multiple Clocks on FPGAs Colin O

Clock Distribution In Fpga First, 16 clocks would consume too much of the available clock routing. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. First, 16 clocks would consume too much of the available clock routing. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. Optimizing clock networks in fpga design involves several. The internal plls provide clock. clock networks play a vital role in ensuring uniform distribution of clock signals. these clocks present several problems.

From www.mikrocontroller.net

Clock Distribution per FPGA Clock Distribution In Fpga First, 16 clocks would consume too much of the available clock routing. The internal plls provide clock. Optimizing clock networks in fpga design involves several. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. a clock in an fpga system is responsible for driving the fpga design and determines how. Clock Distribution In Fpga.

From www.researchgate.net

Clock and reset distribution box. Bottom centre is the Genesys2 FPGA Clock Distribution In Fpga finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. these clocks present several problems. Optimizing clock networks in fpga design involves several. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. clock networks play a. Clock Distribution In Fpga.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Distribution In Fpga these clocks present several problems. clock networks play a vital role in ensuring uniform distribution of clock signals. First, 16 clocks would consume too much of the available clock routing. The internal plls provide clock. Optimizing clock networks in fpga design involves several. finally, clock distribution networks are responsible for delivering the clock signal to individual components. Clock Distribution In Fpga.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Distribution In Fpga clock networks play a vital role in ensuring uniform distribution of clock signals. First, 16 clocks would consume too much of the available clock routing. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. these clocks present several problems. a clock in an fpga system is responsible for. Clock Distribution In Fpga.

From www.youtube.com

Introduction to FPGA Part 4 Clocks and Procedural Assignments Digi Clock Distribution In Fpga The internal plls provide clock. First, 16 clocks would consume too much of the available clock routing. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. these clocks present several problems. finally, clock distribution networks are responsible for delivering the clock signal to individual. Clock Distribution In Fpga.

From slideplayer.com

Zynq Architecture 7Series FPGA Architecture ppt download Clock Distribution In Fpga First, 16 clocks would consume too much of the available clock routing. clock networks play a vital role in ensuring uniform distribution of clock signals. The internal plls provide clock. Optimizing clock networks in fpga design involves several. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run. Clock Distribution In Fpga.

From slideplayer.com

An Introduction to FPGA and SOPC Development Board ppt download Clock Distribution In Fpga Optimizing clock networks in fpga design involves several. clock networks play a vital role in ensuring uniform distribution of clock signals. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. these clocks present several problems. The internal plls provide clock. finally, clock distribution. Clock Distribution In Fpga.

From circuitcellar.com

Optimizing Clock Resources in FPGAs Circuit Cellar Clock Distribution In Fpga Optimizing clock networks in fpga design involves several. First, 16 clocks would consume too much of the available clock routing. clock networks play a vital role in ensuring uniform distribution of clock signals. these clocks present several problems. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can. Clock Distribution In Fpga.

From slideplayer.com

L0TP studies Clock and distribution Scheme Busy handling ppt download Clock Distribution In Fpga clock networks play a vital role in ensuring uniform distribution of clock signals. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. Optimizing clock networks in fpga design involves several. The internal plls provide clock. First, 16 clocks would consume too much of the available clock routing. a clock. Clock Distribution In Fpga.

From www.youtube.com

What is a Clock in an FPGA? YouTube Clock Distribution In Fpga a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. Optimizing clock networks in fpga design involves several. The internal plls provide clock. First, 16 clocks would consume too much of the available clock routing. clock networks play a vital role in ensuring uniform distribution of. Clock Distribution In Fpga.

From www.edaboard.com

Problem with Clock distribution with FPGA Forum for Electronics Clock Distribution In Fpga First, 16 clocks would consume too much of the available clock routing. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. these clocks present several problems. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. . Clock Distribution In Fpga.

From www.slideserve.com

PPT Introduction to FPGA PowerPoint Presentation, free download ID Clock Distribution In Fpga clock networks play a vital role in ensuring uniform distribution of clock signals. First, 16 clocks would consume too much of the available clock routing. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. Optimizing clock networks in fpga design involves several. these clocks present several problems. The internal. Clock Distribution In Fpga.

From www.edaboard.com

Problem with Clock distribution with FPGA Forum for Electronics Clock Distribution In Fpga clock networks play a vital role in ensuring uniform distribution of clock signals. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. First, 16 clocks would consume too much of the available clock routing. these clocks present several problems. The internal plls provide clock. a clock in an. Clock Distribution In Fpga.

From www.researchgate.net

FPGA floor plan/clock architecture. Download Scientific Diagram Clock Distribution In Fpga a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. The internal plls provide clock. First, 16 clocks would consume too much of the available clock routing. clock networks play a vital role in ensuring uniform distribution of clock signals. these clocks present several problems.. Clock Distribution In Fpga.

From colinoflynn.com

Experimenting with Metastability and Multiple Clocks on FPGAs Colin O Clock Distribution In Fpga Optimizing clock networks in fpga design involves several. First, 16 clocks would consume too much of the available clock routing. The internal plls provide clock. clock networks play a vital role in ensuring uniform distribution of clock signals. finally, clock distribution networks are responsible for delivering the clock signal to individual components within the fpga. these clocks. Clock Distribution In Fpga.

From www.slideserve.com

PPT CMS GCT Hardware Wheel Card PowerPoint Presentation ID5093093 Clock Distribution In Fpga a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. Optimizing clock networks in fpga design involves several. clock networks play a vital role in ensuring uniform distribution of clock signals. finally, clock distribution networks are responsible for delivering the clock signal to individual components. Clock Distribution In Fpga.

From www.researchgate.net

Htree clock distribution network for 8x8 FPGA Download Scientific Clock Distribution In Fpga clock networks play a vital role in ensuring uniform distribution of clock signals. The internal plls provide clock. a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. Optimizing clock networks in fpga design involves several. these clocks present several problems. finally, clock distribution. Clock Distribution In Fpga.

From www.pantechsolutions.net

Implementation of Digital Clock using Spartan3an FPGA Evaluation Kit Clock Distribution In Fpga a clock in an fpga system is responsible for driving the fpga design and determines how fast it can run and process. First, 16 clocks would consume too much of the available clock routing. clock networks play a vital role in ensuring uniform distribution of clock signals. The internal plls provide clock. finally, clock distribution networks are. Clock Distribution In Fpga.